## Reduced thermal resistance of the silicon-synthetic diamond composite substrates at elevated temperatures

V. Goyal, S. Subrina, D. L. Nika, and A. A. Balandin<sup>a)</sup>

Department of Electrical Engineering and Materials Science and Engineering Program, Nano-Device Laboratory, Bourns College of Engineering, University of California–Riverside, Riverside, California 92521, USA

(Received 29 May 2010; accepted 21 June 2010; published online 19 July 2010)

The authors report results of experimental investigation of thermal conductivity of synthetic diamond-silicon composite substrates. Although composite substrates are more thermally resistive than silicon at room temperature they *outperform* conventional wafers at elevated temperatures owing to different thermal conductivity dependence on temperature. The crossover point is reached near  $\sim 360~\rm K$  and can be made even lower by tuning the polycrystalline-grain size, film thickness, and interface quality. The reduction of thermal resistance of composite wafers at temperatures, typical for operation of electronic chips, may lead to better thermal management and new *phonon-engineered* methods for the electron mobility enhancement. © 2010 American Institute of Physics. [doi:10.1063/1.3463455]

Most recently, there was a notable renewal of interest in composite silicon-synthetic diamond (Si-Di) substrates as alternatives to conventional silicon (Si) wafers. It is driven by several factors. First, continuing downscaling of Si complementary metal-oxide semiconductor (CMOS) technology and progress in high-power electronics demand more efficient heat removal to handle the increasing power density and rising temperature (T) of hot spots. The high T in the transistor channels translates into degraded mobility,  $\mu$ , and, as a result, leads to smaller speed and drive current. Second, there was a fast progress in the chemical vapor deposition (CVD) of ultrananocrystalline diamond (UNCD) and microcrystalline diamond (MCD) on Si.4 It has been demonstrated that UNCD films can be synthesized at temperatures that CMOS devices can withstand.<sup>5</sup> Additional motivations for Si-Di substrates include prospects of hybrid Si-carbon electronics, which would involve different allotropes of carbon, e.g., diamond, diamond-like carbon, carbon nanotubes, and graphene, 6 as well as proposals for the phonon-engineered mobility enhancement in nanoscale Si channels with dia-

At the same time, the heat conduction properties of synthetic diamond are not nearly as good as those of crystalline diamond. The thermal conductivity, K, of high-quality single-crystal diamond is ~2200 W/mK. The roomtemperature (RT) thermal conductivity of MCD is ~550 W/mK (Ref. 10) while that of UNCD is much smaller than that of Si. 11 The "effective" thermal conductivity,  $K_{\rm eff}$ , defined for the whole MCD/Si and UNCD/Si substrates, depends on the polycrystalline-diamond grain size, diamond layer thickness, and interface quality. The surface roughness for MCD is usually much larger than that for UNCD. The rougher interfaces results in higher thermal boundary resistance, which offsets the thermal conductivity increase due to a lager grain size. Considering that RT thermal conductivity of Si is ~145 W/mK it is not clear if incorporation of synthetic diamond can improve the heat removal at the present state of technology for diamond deposition. For this reason, the conventional belief was that one has to wait for improvements in the CVD diamond until the composite Si-Di wafers become practical for CMOS integration from the thermal management point of view.

In this letter, we show that although composite Si-Di substrates have smaller  $K_{\rm eff}$  than Si at RT they outperform Si wafers at elevated temperatures. The crossover point is reached in the range  $\sim 360-450$  K depending on the grain size and thickness of the synthetic diamond. The temperature when the Si-Di substrates become less thermally resistive is near the operating temperature ( $T \sim 380$  K) of electronic chips 12 and substantially lower than the temperature of hot spots in advanced chips. 3

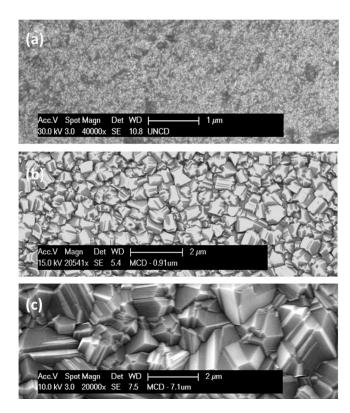

For this study we used a set of samples with UNCD (Advanced Diamond Technologies) and MCD (sp3 Diamond Technologies) layers grown on conventional 100 mm Si wafers. To study the effect of the grain size and film thickness on thermal conductivity, some of the samples had the same grain size, defined by the growth conditions, but different thicknesses while other samples had the same thickness but different grain sizes. The Si-Di wafers were characterized using the scanning electron microscopy (SEM) and Raman spectroscopy under 488-nm laser excitation. The Raman spectra for MCD and UNCD are qualitatively different. The observed features were in line with reported data. 10 The SEM images confirmed the average grain sizes  $d \approx 5-10$  nm for UNCD films [Fig. 1(a)]. The grain sizes for  $\sim 1-\mu$ m-thick and 7- $\mu$ m-thick MCD films were  $d \approx 0.5-0.8 \mu$ m and  $d \approx 1-3 \mu \text{m}$ , respectively [Figs. 1(b) and 1(c)].

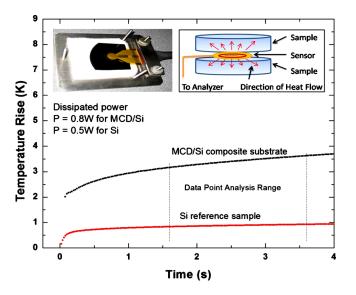

The thermal conductivity measurements were carried out using the transient planar source (TPS) method.  $^{13,14}$  We have previously "calibrated" our TPS system with the 3- $\omega$  method, a standard technique for K measurements of thin films.  $^{15}$  In TPS method, an electrically insulated flat nickel sensor plays a role of the heater and thermometer simultaneously. It is placed between two pieces of a sample under investigation (see inset to Fig. 2). During the measurement, a current pulse is passed through the sensor, which generates heat. Thermal properties of the material are determined by

a) Author to whom correspondence should be addressed. Electronic mail: balandin@ee.ucr.edu.

FIG. 1. Top-view SEM images of synthetic diamond films revealing the grain sizes for (a) UNCD film, (b) MCD film with  $\sim 1~\mu m$  thickness, and (c) MCD film with  $\sim 7~\mu m$  thickness.

recording temperature rise as a function of time using the equation  $^{13}$   $\overline{\Delta T(\tau)} = P(\pi^{3/2}rK)^{-1}D(\tau)$ , where  $\tau = (t_m\alpha/r^2)^{1/2}$ ,  $\alpha$  is the thermal diffusivity,  $t_m$  is the transient measurement time, r is the radius of the sensor, P is the input heating power, and  $D(\tau)$  is the modified Bessel function. The time and the input power are chosen so that the heat flow is within the sample boundaries and the T rise of the sensor is not influenced by the outer boundaries of the sample.  $^{13,16,17}$  In our case, the optimum probing depth was achieved for

FIG. 2. (Color online) Transient temperature rise for the MCD/Si composite substrate and reference Si wafer used for the thermal conductivity extraction. The insets show the thermal sensor positioned on a sample and schematic of the measurements using TPS technique.

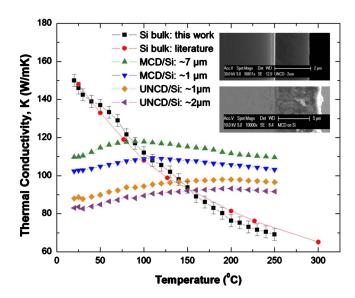

FIG. 3. (Color online) Thermal conductivity as a function of temperature for UNCD/Si and MCD/Si composite substrates, as well as for the reference Si wafer. The insets show the cross-sectional SEM images of UNCD/Si and MCD/Si substrates.

P=0.8 W and P=0.5 W for the composite MCD/Si and reference Si substrates, respectively (Fig. 2).

Figure 3 presents the measured  $K_{\text{eff}}(T)$  for a reference Si wafer, two MCD/Si and two UNCD/Si composite substrates. All examined substrates had distinctively sharp interface between the diamond layer and Si wafer verified by crosssectional SEM (see inset). A comparison with K values for Si from literature 18 indicates an excellent agreement and attests to the accuracy of our measurements. The Si wafer's K scales as  $\sim 1/T$ , which is expected for semiconductor crystals near RT. The  $K_{\text{eff}}(T)$  dependence for MCD/Si (UNCD/ Si) is distinctively different. The thermal conductivity of the composite Si-Di substrates actually grows with temperature from RT to  $\sim 100-200$  °C, depending on the grain size and thickness of the diamond layer. The unexpected observation is that the crossover point, where  $K_{\text{eff}}$  of the composite substrates becomes larger than that of conventional Si wafers, is reached at rather low  $T \approx 75-150$  °C. The examined MCD/Si substrates start to outperform Si wafers sooner than UNCD/Si substrates. The crossover point shifts to lower T with increasing thickness of MCD layer. This is an important observation, which means that the composite Si-Di wafers can be less thermally resistive at the operating temperature of the state-of-the-art electronic chips and high-power devices.

The physics behind the lower thermal resistivity of Si-Di wafers at elevated temperatures is related to differences in K(T) dependence of crystalline Si and UNCD or MCD. In bulk crystals, K is limited by the crystal anharmonicity via the phonon Umklapp scattering, which results in 1/T dependence. In polycrystalline materials K increases with T or depends only weakly on T. The changed T dependence can be explained by various theoretical models, e.g., using a conventional Callaway–Klemens approach, where scattering on grains is the dominant phonon relaxation mechanism, <sup>19,20</sup> or the phonon-hopping model, <sup>21</sup> which predicts higher rates of the phonon grain-to-grain transmissions with increasing T. To analyze our results we determined the thermal conductivity,  $K_{\rm Di}$ , of the synthetic diamond layers themselves from the equation  $L/K_{\rm eff} = L_{\rm Si}/K_{\rm Si} + L_{\rm Di}/K_{\rm Di}$ , where  $L = L_{\rm Si} + L_{\rm Di}$  is the

total thickness of the composite substrate,  $K_{Si}$  is the thermal conductivity of the Si wafer, and  $L_{Si}$  ( $L_{Di}$ ) is the thickness of the Si wafer (diamond layer). Here we neglected TBR at the Si/Di interface, which is much smaller than  $L_{Si}/K_{Si}$  or  $L_{\rm Di}/K_{\rm Di}$  as estimated by applying the above equation to two samples with the same type of diamond layer but different thickness  $L_{Di}$ . We then calculated the interfacial grain-tograin thermal conductance  $G = (K_D/d)[1/(K_D/K_{Di}-1)],$ where  $K_D$  is the thermal conductivity inside the grain assumed to be equal to the crystalline diamond's bulk value. For our UNCD layers we found  $G \sim 50-100$  MW/m<sup>2</sup> K for the grain diameter  $d \sim 5-10\,$  nm at RT. G grows with T and can be approximated as  $G(T)(MW/m^2 K) \approx 81.2 + 1.65$  $\times 10^{-4} T^3$  (°C) for  $d \sim 5$  nm. The  $G(T) \sim T^3$  dependence is consistent with the Kapitza thermal resistance behavior.<sup>23</sup> The obtained values fall within the conventionally accepted range  $G \sim 20-200$  MW/m<sup>2</sup> K for the interface conductance between dissimilar materials near RT.<sup>24</sup> Our analysis suggests that Si-Di composite substrates even with nonperfect grain interfaces perform better than Si for heat removal at elevated temperatures.

To obtain estimates for the electron mobility enhancement as a result of higher  $K_{\rm eff}$  of Si-Di substrates we simulated T profiles in the examined wafers. The heat diffusion equation for given structures was solved numerically by the finite-element method using COMSOL software. The devices were modeled as heat sources with the power density and geometry chosen in such a way so that the resulting temperature rise is close to the typical values in state-of-the-art chips. The Si wafers were then replaced with the Si-Di substrates and modeled with the experimentally determined  $K_{\text{eff}}(T)$ . The difference in the device-channel temperature rise,  $\Delta T_m$ , between Si wafers and Si-Di substrates was translated into the carrier mobility values using the expression  $\mu(T) \sim T^{-n}$ , where  $n \sim 2.42$  for Si. <sup>25,26</sup> We found that for realistic parameters one can obtain a reduction  $\Delta T_m \sim 20-40$  °C, which can result in up to  ${\sim}20\%$  mobility increase. The  $\mu$  increase can be made larger via improvement of Si-Di substrates quality, increase in  $L_{Di}$  for MCD, and increase in G for UNCD and MCD. The currently used methods for the mobility improvement in Si CMOS use SiGe alloys to strain the device channels.<sup>27</sup> The alloys are characterized by very low K.<sup>28</sup> The mobility, which can be achieved in chips implemented on Si-Di substrates, will not be prone to degradation due to higher thermal resistance. The decrease of the channel temperature due to a lower thermal resistance of the composite substrates at elevated temperatures will also improve chips' reliability and life-time. Another benefit of using diamond with Si is a continuing drive for carbon electronics. Carbon materials are characterized by a very wide range of K, from the highest in graphene<sup>29</sup> to the lowest in disordered carbons,<sup>30</sup> and can provide both thermally conductive and insulating interfaces.

In conclusion, we demonstrated that composite Sidiamond substrates, which are more thermally resistive than Si at RT, *outperform* Si at elevated temperatures characteristic for operation of the high-power and state-of-the-art electronics. The benefits of the composite substrates increase with chips' growing power density and hot-spot tempera-

tures. We elucidated physical processes leading to the improved thermal properties of the composite substrates and outlined the strategy for achieving mobility enhancement via thermal, i.e., phonon flux, engineering.

The work at UCR was supported through ARL/AFOSR Award No. FA9550-08-1-0100 (Program Director: Dr. K. Reinhardt) on Electron and Phonon Engineered Nano- and Heterostructures for Performance Enhancement of Electronic and Optoelectronic Devices. The SEM characterization was carried out at UCR CFAMM facilities.

<sup>1</sup>A. Vassighi and M. Sachdev, *Springer Science and Business Media* (Springer, New York, 2005).

<sup>2</sup>S. P. Gurrum, S. K. Suman, Y. K. Joshi, and A. G. Fedorov, IEEE Trans. Device Mater. Reliab. **4**, 709 (2004).

<sup>3</sup>A. A. Balandin, "New Materials and Designs can Keep Chips Cool," invited feature, IEEE Spectrum, October 2009, p. 29.

<sup>4</sup>A. V. Sumant, O. Auciello, R. W. Carpick, S. Srinivasan, and J. E. Butler, MRS Bull. 35, 281 (2010).

<sup>5</sup>X. Xiao, J. Birrell, J. E. Gerbi, O. Auciello, and J. A. Carlisle, J. Appl. Phys. **96**, 2232 (2004).

<sup>6</sup>A. Geim, Science **324**, 1530 (2009).

<sup>7</sup>V. A. Fonoberov and A. A. Balandin, Nano Lett. 6, 2442 (2006).

<sup>8</sup>D. L. Nika, E. P. Pokatilov, and A. A. Balandin, Appl. Phys. Lett. 93, 173111 (2008).

<sup>9</sup>R. Berman, P. R. W. Hudson, and M. Martinez J. Phys. C 8, L430 (1975); A. V. Sukhadolau, E. V. Ivakin, V. G. Ralchenko, A. V. Khomich, A. V. Vlasov, and A. F. Popovich, Diamond Relat. Mater. 14, 589 (2005).

<sup>10</sup>M. Shamsa, S. Ghosh, I. Calizo, V. Ralchenko, A. Popovich, and A. A. Balandin, J. Appl. Phys. **103**, 083538 (2008).

<sup>11</sup>W. L. Liu, M. Shamsa, I. Calizo, A. A. Balandin, V. Ralchenko, A. Popovich, and A. Saveliev, Appl. Phys. Lett. 89, 171915 (2006).

<sup>12</sup>J. Tsai, C. Chen, G. Chen, B. Goplen, H. Qian, Y. Zhan, S. Kang, M. Wong, and S. Sapatnekar, Proc. IEEE 94, 1502 (2006).

<sup>13</sup>S. E. Gustafsson, Rev. Sci. Instrum. **62**, 797 (1991).

<sup>14</sup>S. Ghosh, D. Teweldebrhan, J. R. Morales, J. E. Garay, and A. A. Balandin, J. Appl. Phys. **106**, 113507 (2009).

<sup>15</sup>D. G. Cahill, Rev. Sci. Instrum. **61**, 802 (1990).

<sup>16</sup>S. E. Gustafsson, E. Karawacki, and M. A. Chohan, J. Phys. D 19, 727 (1986).

<sup>17</sup>M. Gustavsson, H. Wang, R. M. Trejo, E. Lara-Curzio, R. B. Dinwiddie, and S. E. Gustafsson, Int. J. Thermophys. 27, 1816 (2006).

<sup>18</sup>C. Y. Ho, R. W. Powell, and P. E. Liley, J. Phys. Chem. Ref. Data 3, I-588 (1974).

<sup>19</sup>A. Khitun, A. Balandin, J. L. Liu, and K. L. Wang, J. Appl. Phys. 88, 696 (2000); Superlattices Microstruct. 30, 1 (2001).

<sup>20</sup>J. L. Liu, A. Khitun, K. L. Wang, W. L. Liu, G. Chen, Q. H. Xie, and S. G. Thomas, Phys. Rev. B **67**, 165333 (2003).

<sup>21</sup>L. Braginsky, N. Lukzen, V. Shklover, and H. Hofmann, Phys. Rev. B 66, 134203 (2002).

<sup>22</sup>H. S. Yang, G.-R. Bai, L. J. Thopmson, and J. A. Eastman, Acta Mater. 50, 2309 (2002).

<sup>23</sup>E. T. Swartz and R. O. Pohl, Rev. Mod. Phys. **61**, 605 (1989).

<sup>24</sup>D. G. Cahill, K. Goodson, and A. Majumdar, ASME Trans. J. Heat Transfer 124, 223 (2002).

<sup>25</sup>S. M. Sze, *Physics of Semiconductor Devices* (Wiley, New York, 1981), p. 28

<sup>26</sup>J. Batista, A. Mandelis, and D. Shaughnessy, Appl. Phys. Lett. 82, 4077 (2003).

<sup>27</sup>H.-S. P. Wong, IBM J. Res. Dev. **46**, 133 (2002).

<sup>28</sup>B. Abeles, Phys. Rev. **131**, 1906 (1963); W. L. Liu and A. A. Balandin, J. Appl. Phys. **97**, 073710 (2005).

<sup>29</sup>S. Ghosh, I. Calizo, D. Teweldebrhan, E. P. Pokatilov, D. L. Nika, A. A. Balandin, W. Bao, F. Miao, and C. N. Lau, Appl. Phys. Lett. **92**, 151911 (2008).

M. A. Makeev and D. Srivastava, Appl. Phys. Lett. 95, 181908 (2009);

M. Shamsa, W. L. Liu, A. A. Balandin, C. Casiraghi, W. I. Milne, and A. C. Ferrari, Appl. Phys. Lett. 89, 161921 (2006).